You are here

Design Description

ASIC design descriptions are written by designers at different levels of abstraction. Most common hardware description languages used by designers are Verilog and VHDL. Both these languages are equally capable of providing complex constructs to describe complex functionality. Behavioral modeling forms highest level of abstraction.

Behavioral description

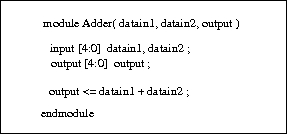

At initial stage of design process designer provides a Behavioral description of the functionality intended. Behavioral model does not care about the structure of the design, combinational or sequential elements used in the design, clock signal and the timing constraints involved. It captures the intended behavior of the design. The below given example describes the behaviour of an adder that adds two four digit inputs to return and output. It is important to note that this description does not capture timing information.

Figure 1: Behavioral modelling

RTL description

RTL stands for Register Transfer Level. In this model the entire design is split into registers with flow of information between these registers at each clock cycle. RTL description captures the change in design at each clock cycle. All the registers are updated at the same time in a clock cycle. Typically an RTL description divides design into registers and the logic blocks that join those registers together. RTL captures the data flow but fails to give a good description of control flow.

Figure 2: Register Transfer Level description of a design.

Structural Description

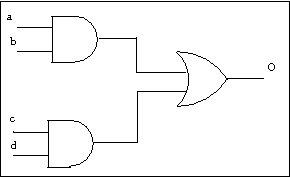

Structural description consists of a network of instances of logic gates and registers described by a technology library. Technology library is provided by fabrication houses.Technology library is a description of simple AND, OR, NOT and complicated multiple functionality cells. The description of a cell includes its geometry, delay and power characteristics.

Structural modelling describes circuit in form of instances of cells and interconnect between those cells.

Figure 3 : structural modelling.